### LNBH26LS

# Dual LNBS supply and control IC with step-up and I2C interface

Datasheet - production data

#### **Features**

- Complete interface between then LNB and l<sup>2</sup>C bus

- Built-in DC-DC converter for single 12 V supply operation and high efficiency (typ. 93% @ 0.5 A)

- Selectable output current limit by external resistor

- Compliant with main satellite receiver output voltage specification (8 programmable levels)

- Accurate built-in 22 kHz tone generator suits widely accepted standards

- 22 kHz tone waveform integrity guaranteed also at no load condition

- Low drop post regulator and high efficiency step-up PWM with integrated power NMOS allowing low power losses

- Overload and overtemperature internal protection with I<sup>2</sup>C diagnostic bits

- LNB short-circuit dynamic protection

- +/- 4 kV ESD tolerant on output power pins

#### **Applications**

- STB satellite receivers

- TV satellite receivers

- PC card satellite receivers

#### Description

Intended for analog and digital dual satellite receiver/Sat-TV, Sat-PC cards, the LNBH26LS is a monolithic voltage regulator and IC interface, assembled in QFN24 (4x4 mm) specifically designed to provide the 13/18 V power supply and the 22 kHz tone signaling to the LNB downconverter in the antenna dishes or to the multiswitch box. In this application field, it offers a complete solution for dual tuner satellite receivers with extremely low component count, low power dissipation together with simple design and I<sup>2</sup>C standard interfacing.

**Table 1: Device summary**

| Order code     | Package  | Packing       |

|----------------|----------|---------------|

| LNBH26LSPQR    | QFN24    | Tape and reel |

| LINDI IZOLOFQK | (4x4 mm) | rape and reei |

Contents LNBH26LS

### Contents

| 1        | Block di               | agram                                                               | 6   |

|----------|------------------------|---------------------------------------------------------------------|-----|

| 2        | Applicat               | tion information (valid for each section A/B)                       | 7   |

|          | 2.1                    | DISEQC™ data encoding (DSQIN pin)                                   | 7   |

|          | 2.2                    | Data encoding by external 22 kHz tone TTL signal                    | 7   |

|          | 2.3<br>DSQII           | Data encoding by external DiSEqC envelope control through the N pin | 8   |

|          | 2.4                    | Output current limit selection                                      | 8   |

|          | 2.5                    | Output voltage selection                                            | 8   |

|          | 2.6                    | Diagnostic and protection functions                                 | 8   |

|          | 2.7                    | Surge protection and TVS diodes                                     | 9   |

|          | 2.8                    | Power-on I <sup>2</sup> C interface reset and undervoltage lockout  | 9   |

|          | 2.9                    | PNG: input voltage minimum detection                                | 9   |

|          | 2.10                   | COMP: boost capacitors and inductor                                 | 9   |

|          | 2.11                   | OLF: overcurrent and short-circuit protection and diagnostic        | .10 |

|          | 2.12                   | OTF: thermal protection and diagnostic                              | .10 |

|          | Pin conf               | figuration                                                          | .11 |

|          | Maximu                 | m ratings                                                           | 14  |

| )        |                        | application circuits                                                |     |

| <b>;</b> | I <sup>2</sup> C bus i | interface                                                           | 17  |

|          | 6.1                    | Data validity                                                       | .17 |

|          | 6.2                    | Start and stop condition                                            |     |

|          | 6.3                    | Byte format                                                         |     |

|          | 6.4                    | Acknowledge                                                         |     |

|          | 6.5                    | Transmission without acknowledge                                    | .17 |

|          | I <sup>2</sup> C inter | face protocol                                                       |     |

|          | 7.1                    | Write mode transmission                                             | .19 |

|          | 7.2                    | Read mode transmission                                              | .20 |

|          | 7.3                    | Data registers                                                      |     |

|          | 7.4                    | Status registers                                                    |     |

|          | Electrica              | al characteristics                                                  |     |

|          | 8.1                    | Output voltage selection                                            |     |

|          | _                      | e information                                                       |     |

|          | i donage               |                                                                     |     |

|          |                        |                                                                     |     |

| LNB | H26LS   |                                     | Contents |

|-----|---------|-------------------------------------|----------|

|     | 9.1     | QFN24L (4x4 mm) package information | 30       |

|     | 9.2     | QFN24L (4x4 mm) packing information | 32       |

| 10  | Revisio | n history                           | 34       |

List of tables LNBH26LS

### List of tables

| Table 1: Device summary                                               |    |

|-----------------------------------------------------------------------|----|

| Table 2: Pin description                                              |    |

| Table 3: Absolute maximum ratings                                     |    |

| Table 4: Thermal data                                                 |    |

| Table 5: LNBH26LS DiSEqC 1.x bill of material                         | 16 |

| Table 6: DATA 1 (read/write register. Register address = 0X2)         | 21 |

| Table 7: DATA 2 (read/write register. Register address = 0X3)         |    |

| Table 8: DATA 3 (read/write register. Register address = 0X4)         | 22 |

| Table 9: DATA 4 (read/write register. Register address = 0X5)         | 23 |

| Table 10: STATUS 1 (read register. Register address = 0X0)            | 23 |

| Table 11: STATUS 2 (read register. Register address = 0X1)            | 24 |

| Table 12: Electrical characteristics of section A/B                   | 25 |

| Table 13: Output voltage selection table (data1 register, write mode) | 27 |

| Table 14: I <sup>2</sup> C electrical characteristics                 | 27 |

| Table 15: Address pin characteristics                                 | 28 |

| Table 16: QFN24L (4x4 mm) package mechanical data                     | 31 |

| Table 17: QFN24L (4x4 mm) tape mechanical data                        | 32 |

| Table 18: QFN24L (4x4 mm) reel mechanical data                        | 33 |

| Table 10: Decument revision history                                   | 24 |

LNBH26LS List of figures

# List of figures Figure 1: Block diagram

| Figure 1: Block diagram                                                        | 6  |

|--------------------------------------------------------------------------------|----|

| Figure 2: Tone enable and disable timing (using an external waveform)          | 7  |

| Figure 3: Tone enable and disable timing (using envelope signal)               | 8  |

| Figure 4: Surge protection circuit                                             | 9  |

| Figure 5: Pin connections (top view)                                           | 11 |

| Figure 6: LNBH26LS DiSEqC 1.X typical application circuit                      |    |

| Figure 7: Data validity on the I2C bus                                         | 18 |

| Figure 8: Timing diagram of I <sup>2</sup> C bus                               | 18 |

| Figure 9: Acknowledge on the I2C bus                                           | 18 |

| Figure 10: Example of writing procedure starting with first data address 0x2   | 19 |

| Figure 11: Example of reading procedure starting with first status address 0X0 | 20 |

| Figure 12: QFN24L (4x4 mm) package outline                                     | 30 |

| Figure 13: QFN24L (4x4 mm) recommended footprint                               | 31 |

| Figure 14: QFN24L (4x4 mm) tape outline                                        |    |

| Figure 15: QFN24L (4x4 mm) reel outline                                        | 33 |

Block diagram LNBH26LS

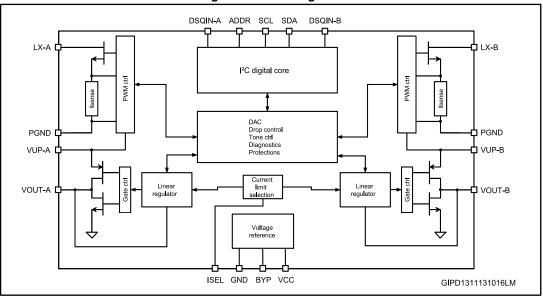

# 1 Block diagram

Figure 1: Block diagram

### 2 Application information (valid for each section A/B)

This IC has a built-in DC-DC step-up converter that, from a single source (8 V to 16 V), generates the voltages (VUP) that let the integrated LDO post-regulator (generating the 13 V/18 V LNB output voltages plus the 22 kHz DiSEqC tone) work with a minimum dissipated power of 0.5 W typ. @ 500 mA load (the LDO drop voltage is internally kept at VUP - VOUT = 1 V typ.). The IC is also provided with an undervoltage lockout circuit that disables the whole circuit when the supplied VCC drops below a fixed threshold (4.7 V typically). The step-up converter soft-start function reduces the in-rush current during startup. The SS time is internally fixed at 4 ms typ. to switch from 0 to 13 V and 6 ms typ. to switch from 0 to 18 V.

### 2.1 DISEQC™ data encoding (DSQIN pin)

The internal 22 kHz tone generator is factory trimmed in accordance with the DiSEqC™ standards, and can be activated in 3 different ways:

- 1) By an external 22 kHz source DiSEqC<sup>™</sup> data connected to the DSQIN logic pin (TTL compatible). In this case the I<sup>2</sup>C tone control bits must be set: EXTM=TEN=1.

- 2) By an external DiSEqC<sup>™</sup> data envelope source connected to the DSQIN logic pin. In this case the I<sup>2</sup>C tone control bits must be set: EXTM=0 and TEN=1.

- 3) Through the TEN I<sup>2</sup>C bit if the 22 kHz presence is requested in continuous mode. In this case the DSQIN TTL pin must be pulled high and the EXTM bit set to "0".

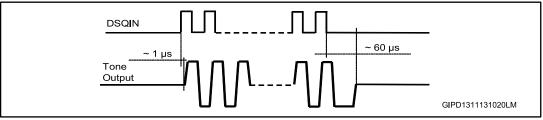

### 2.2 Data encoding by external 22 kHz tone TTL signal

In order to improve design flexibility, an external tone signal can be input to the DSQIN pin by setting the EXTM bit to "1".

The DSQIN is a logic input pin which activates the 22 kHz tone to the VOUT pin, by using the LNBH26LS integrated tone generator.

The output tone waveforms are internally controlled by the LNBH26LS tone generator in terms of rise/fall time and tone amplitude, while, the external 22 kHz signal on the DSQIN pin is used to define the frequency and the duty cycle of the output tone. A TTL compatible 22 kHz signal is required for the proper control of the DSQIN pin function. Before sending the TTL signal on the DSQIN pin, the EXTM and TEN bits must be previously set to "1". As soon as the DSQIN internal circuit detects the 22 kHz TTL external signal code, the LNBH26LS activates the 22 kHz tone on the VOUT output with about 1 µs delay from TTL signal activation, and it stops with about 60 µs delay after the 22 kHz TTL signal on DSQIN has expired. Refer to Figure 2: "Tone enable and disable timing (using an external waveform)".

Figure 2: Tone enable and disable timing (using an external waveform)

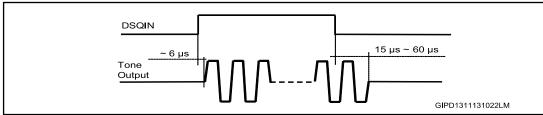

# 2.3 Data encoding by external DiSEqC envelope control through the DSQIN pin

If an external DiSEqC™ envelope source is available, the internal 22 kHz generator can be activated during the tone transmission by connecting the DiSEqC™ envelope source to the DSQIN pin. In this case the I²C tone control bits must be set: EXTM=0 and TEN=1. In this manner, the internal 22 kHz signal is superimposed to the VOUT DC voltage to generate the LNB output 22 kHz tone. During the period in which the DSQIN is kept high the internal control circuit activates the 22 kHz tone output.

The 22 kHz tone on the VOUT pin is activated with about 6 µs delay from the DSQIN TTL signal rising edge, and it stops with a delay time in the range from 15 µs to 60 µs after the 22 kHz TTL signal on DSQIN has expired, refer to *Figure 3: "Tone enable and disable timing (using envelope signal)"*).

Figure 3: Tone enable and disable timing (using envelope signal)

### 2.4 Output current limit selection

The linear regulator current limit threshold can be set by an external resistor connected to the ISEL pin. The resistor value defines the output current limit as per below equation:

#### **Equation 1:**

$$I_{LIM}$$

(typ.)=  $\frac{16578}{RSEL^{1.206}}$

with ISET = 0,

where RSEL is the resistor connected between ISEL and GND expressed in kW and  $I_{LIM}$ (typ.) is the typical current limit threshold expressed in mA.  $I_{LIM}$  can be set up to 750 mA for each channel. However, do not exceed, for a long period of time, a total amount of current of 1 A from both sections (IOUT-A + IOUT-B < 1 A) in order to avoid the overtemperature protection triggering and to thoroughly validate the PCB layout thermal management in real application environment conditions.

### 2.5 Output voltage selection

Each linear regulator channel output voltage level can be easily programmed to accomplish application specific requirements, using 4 + 4 bits of an internal DATA1 register, see Section 7.3: "Data registers" and Table 13: "Output voltage selection table (data1 register, write mode)" for exact programmable values. Register writing is accessible via the I<sup>2</sup>C bus.

### 2.6 Diagnostic and protection functions

The LNBH26LS has 4 diagnostic internal functions provided via the I<sup>2</sup>C bus, by reading 4 bits on the STATUS1 register (in read mode). All the diagnostic bits are, in normal operation (that is, no failure detected), set to low. One diagnostic bit is dedicated to the

GIPD1311131146LM

overtemperature (OTF), and two bits (one per section) are dedicated to overcurrent (OLF-A, OLF-B). One bit is dedicated to the input voltage power not good function (PNG). Once the OTF bit (or OLF-A, OLF-B or PNG) has been activated (set to "1"), it is latched to "1" until the relevant cause is removed and a new register reading operation is performed.

#### 2.7 Surge protection and TVS diodes

Each LNBH26LS device section is directly connected to the antenna cable in a set-top box. Atmospheric phenomenon can cause high voltage discharges on the antenna cable causing damage to the attached devices. Surge pulses occur due to direct or indirect lightning strikes to an external (outdoor) circuit. This leads to currents or electromagnetic fields causing high voltage or current transients. Transient voltage suppressor (TVS) devices are usually placed, as shown in the following schematic, to protect each section of STB output circuits where the LNBH26LS and other devices are electrically connected to the antenna cable.

to LNB IF connector

VUP

VOUT

LNBH26S

LNBH26S

Figure 4: Surge protection circuit

For this purpose the use of LNBTVSxx surge protection diodes specifically designed by ST is recommended. The selection of the LNBTVS diode should be made based on the maximum peak power dissipation that the diode is capable of supporting (see the LNBTVS datasheet for further details).

### 2.8 Power-on I<sup>2</sup>C interface reset and undervoltage lockout

The I²C interface built into the LNBH26LS is automatically reset at power-on. As long as the VCC stays below the undervoltage lockout (UVLO) threshold (4.7 V typ.), the interface does not respond to any I²C command and all data register bits are initialized to zero, therefore keeping the power blocks disabled. Once the VCC rises above 4.8 V typ., the I²C interface becomes operative and the DATA registers can be configured by the main microprocessor.

### 2.9 PNG: input voltage minimum detection

When the input voltage (VCC pin) is lower than LPD (low power diagnostic) minimum thresholds, the PNG I<sup>2</sup>C bit is set to "1". Refer to the *Table 14: "I<sup>2</sup>C electrical characteristics"* for threshold details.

### 2.10 COMP: boost capacitors and inductor

The DC-DC converter compensation loop can be optimized in order to properly work with both ceramic and electrolytic capacitors (VUP pin). For this purpose, one I<sup>2</sup>C bit in the DATA 4 register (see COMP not found) can be set to "1" or "0" as follows:

COMP = 0 for electrolytic capacitors

COMP = 1 for ceramic capacitors

For recommended DC-DC capacitor and inductor values refer to Section 5: "Typical application circuits" and to the BOM in Table 5: "LNBH26LS DiSEqC 1.x bill of material".

#### 2.11 OLF: overcurrent and short-circuit protection and diagnostic

In order to reduce the total power dissipation during an overload or a short-circuit condition, each section of the device is provided with a dynamic short-circuit protection. The shortcircuit current protection can be set either statically (simple current clamp) or dynamically through the corresponding PCL bit of the I2C DATA3 register. When the PCL (pulsed current limiting) bit is set to low, the overcurrent protection circuit works dynamically: as soon as an overload is detected, the output current is provided for T<sub>ON</sub> time 90 ms and after that, the output is set as shutdown for a T<sub>OFF</sub> time of typically 900 ms. Simultaneously, the corresponding diagnostic OLF I<sup>2</sup>C bit of the STATUS1 register is set to "1". After this time has elapsed, the involved output is resumed for a time T<sub>ON</sub>. At the end of T<sub>ON</sub>, if the overload is still detected, the protection circuit cycles again through T<sub>OFF</sub> and T<sub>ON</sub>. At the end of a full T<sub>ON</sub> in which no overload is detected, normal operation is resumed and the OLF diagnostic bit is reset to low after the register reading. Typical T<sub>ON</sub>+ T<sub>OFF</sub> time is 990 ms and is determined by an internal timer. This dynamic operation can greatly reduce the power dissipation in short-circuit condition, ensuring an excellent power-on startup in most conditions. However, there may be some cases in which a highly capacitive load on the output can cause a difficult startup when the dynamic protection is chosen. This can be solved by initiating any power startup in static mode (PCL =1) and, then, switching to the dynamic mode (PCL = 0) after a chosen amount of time depending on the output capacitance. Also in static mode, the diagnostic OLF bit goes to "1" when the current clamp limit is reached and returns low when the overload condition is cleared and register reading is performed.

After the overload condition is removed, normal operation can be resumed in two ways, according to the OLR I<sup>2</sup>C bit on the DATA4 register.

If OLR=1, all VSEL bits, corresponding to the involved section, are reset to "0" and the LNB section output (VOUT pin) is disabled. To re-enable the output stage, the VSEL bits must be set again by the microprocessor and the OLF bit is reset to "0" after a register reading operation.

If OLR=0, the involved output is automatically re-enabled as soon as the overload condition is removed, and the OLF bit is reset to "0" after a register reading operation.

### 2.12 OTF: thermal protection and diagnostic

The LNBH26LS is also protected against overheating: when the junction temperature exceeds 150 °C (typ.), the step-up converter and both linear regulators are shut off, the diagnostic OTF bit in the STATUS1 register is set to "1". After the overtemperature condition is removed, normal operation can be resumed in two ways, according to the THERM I<sup>2</sup>C bit on the DATA4 register.

If THERM=1, all VSEL bits are reset to "0" and both LNB outputs (VOUT pins) are disabled. To re-enable the output stages, the VSEL bits must be set again by the microprocessor, while the OTF bit is reset to "0" after a register reading operation.

If THERM=0, outputs are automatically re-enabled as soon as the overtemperature condition is removed, while the OTF bit is reset to "0" after a register reading operation.

LNBH26LS Pin configuration

# 3 Pin configuration

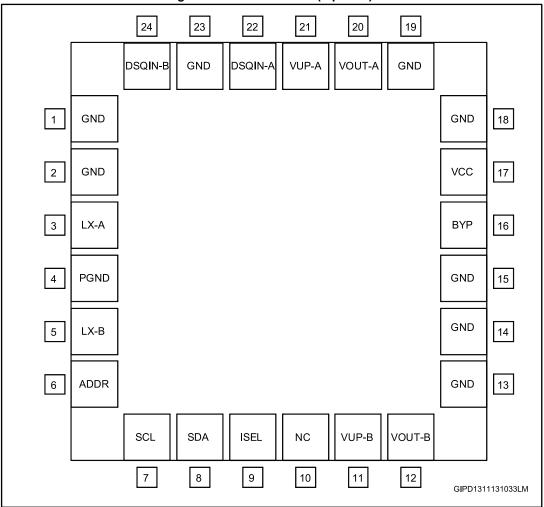

Figure 5: Pin connections (top view)

Pin configuration LNBH26LS

Table 2: Pin description

| Table 2: Pin description              |        |                                             |                                                                                                                                                                                                                                                                    |  |  |

|---------------------------------------|--------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin n°                                | Symbol | Name                                        | Pin function                                                                                                                                                                                                                                                       |  |  |

| 3                                     | LX-A   | NMOS drain                                  | Channel A, integrated N-channel power MOSFET drain.                                                                                                                                                                                                                |  |  |

| 4                                     | P-GND  | Power ground                                | DC-DC converter power ground. To be connected directly to the exposed pad.                                                                                                                                                                                         |  |  |

| 5                                     | LX-B   | NMOS drain                                  | Channel B, integrated N-channel power MOSFET drain.                                                                                                                                                                                                                |  |  |

| 6                                     | ADDR   | Address setting                             | Two I <sup>2</sup> C bus addresses available by setting the ADDRESS pin level voltage. See <i>Table 15: "Address pin characteristics"</i> .                                                                                                                        |  |  |

| 7                                     | SCL    | Serial clock                                | Clock from I <sup>2</sup> C bus.                                                                                                                                                                                                                                   |  |  |

| 8                                     | SDA    | Serial data                                 | Bi-directional data from/to I <sup>2</sup> C bus.                                                                                                                                                                                                                  |  |  |

| 9                                     | ISEL   | Current selection<br>for channel A<br>and B | The resistor "RSEL" connected between ISEL and GND defines the linear regulator current limit threshold. Refer to Section 2: "Application information (valid for each section A/B)". The RSEL resistor defines the same current limit for both channels (A and B). |  |  |

| 1, 2, 13,<br>14, 15,<br>18, 19,<br>23 | GND    | Analog ground                               | Analog circuit ground. To be connected directly to the exposed pad.                                                                                                                                                                                                |  |  |

| 10                                    | NC     | Not internally connected                    | Not internally connected pin. Set floating if not used.                                                                                                                                                                                                            |  |  |

| 11                                    | VUP-B  | Channel B step-up voltage                   | Input of channel B linear post-regulator. The voltage on this pin is monitored by the internal channel B step-up controller to keep a minimum dropout across the linear pass transistor.                                                                           |  |  |

| 12                                    | VOUT-B | Channel B,<br>LNB output port               | Output of channel B integrated very low drop linear regulator. Refer to <i>Table 13:</i> "Output voltage selection table (data1 register, write mode)" for voltage selection and description.                                                                      |  |  |

| 16                                    | ВҮР    | Bypass capacitor                            | Needed for internal pre-regulator filtering. The BYP pin is intended only to connect an external ceramic capacitor. Any connection of this pin to an external current or voltage sources may cause permanent damage to the device.                                 |  |  |

| 17                                    | VCC    | Supply input                                | 8 to 16 V IC DC-DC power supply.                                                                                                                                                                                                                                   |  |  |

| 20                                    | VOUT-A | Channel A,<br>LNB output port               | Output of channel A integrated very low drop linear regulator. Refer to <i>Table 13:</i> "Output voltage selection table (data1 register, write mode)" for voltage selection and description.                                                                      |  |  |

| 21                                    | VUP-A  | Channel A step-up voltage                   | Input of channel A linear post-regulator. The voltag on this pin is monitored by the internal channel A step-up controller to keep a minimum dropout acros the linear pass transistor.                                                                             |  |  |

LNBH26LS Pin configuration

| Pin n° | Symbol  | Name                                                                        | Pin function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|---------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22     | DSQIN-A | DSQIN for<br>DiSEqC<br>envelope input<br>or<br>external 22 KHz<br>TTL input | It is intended for channel A 22 kHz tone control.  It can be used as DiSEqC envelope input or external 22 kHz TTL input depending on the EXTM-A I²C bit setting as follows:  If EXTM-A=0, TEN-A=1: it accepts the DiSEqC envelope code from the main microcontroller. The LNBH26LS uses this code to modulate the internally generated 22 kHz carrier.  If EXTM-A=TEN-A=1: it accepts external 22 kHz logic signals which activate the 22 kHz tone output, refer to Section 2.2: "Data encoding by external 22 kHz tone TTL signal".  Pull up high if the tone output is activated only by the TEN-A I²C bit. |

| 24     | DSQIN-B | DSQIN for<br>DiSEqC<br>envelope input<br>or<br>external 22 KHz<br>TTL input | It is intended for channel B 22 kHz tone control.  It can be used as DiSEqC envelope input or external 22 kHz TTL input depending on the EXTM-B I²C bit setting as follows:  If EXTM-B=0, TEN-B=1: it accepts the DiSEqC envelope code from the main microcontroller. The LNBH26LS uses this code to modulate the internally generated 22 kHz carrier.  If EXTM-A=TEN-A=1: it accepts external 22 kHz logic signals which activate the 22 kHz tone output, refer to Section 2.2: "Data encoding by external 22 kHz tone TTL signal".  Pull up high if the tone output is activated by TEN-B I²C bit only.     |

| Epad   | Epad    | Exposed pad                                                                 | To be connected with power grounds and to the ground layer through vias to dissipate the heat.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Maximum ratings LNBH26LS

### 4 Maximum ratings

**Table 3: Absolute maximum ratings**

| Symbol           | Parameter                                                                       | Value              | Unit |

|------------------|---------------------------------------------------------------------------------|--------------------|------|

| Vcc              | DC power supply input voltage pins                                              | -0.3 to 20         | V    |

| V <sub>UP</sub>  | DC input voltage                                                                | -0.3 to 40         | V    |

| I <sub>OUT</sub> | Output current                                                                  | Internally limited | mA   |

| V <sub>OUT</sub> | DC output pin voltage                                                           | -0.3 to 40         | V    |

| VI               | Logic input pin voltage (SDA, SCL, DSQIN, ADDR pins)                            | -0.3 to 7          | V    |

| LX               | LX input voltage                                                                | -0.3 to 30         | V    |

| $V_{BYP}$        | Internal reference pin voltage                                                  | -0.3 to 4.6        | V    |

| ISEL             | Current selection pin voltage                                                   | -0.3 to 3.5        | V    |

| T <sub>STG</sub> | Storage temperature range                                                       | -50 to 150         | °C   |

| TJ               | Operating junction temperature range                                            | -25 to 125         | °C   |

| ESD              | ESD rating with human body<br>model (HBM) all pins, unless<br>power output pins | 2                  | kV   |

| ESD              | ESD rating with human body model (HBM) for power output pins                    | 4                  | KV   |

Table 4: Thermal data

| Symbol            | Parameter                                                                                                                     | Value | Unit |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|------|

| $R_{thJC}$        | Thermal resistance junction-case                                                                                              | 2     | °C/W |

| R <sub>thJA</sub> | Thermal resistance junction-ambient with device soldered on 2s2p 4-layer PCB provided with thermal vias below the exposed pad | 40    | °C/W |

Absolute maximum ratings are those values beyond which damage to the device may occur. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to the network ground terminal.

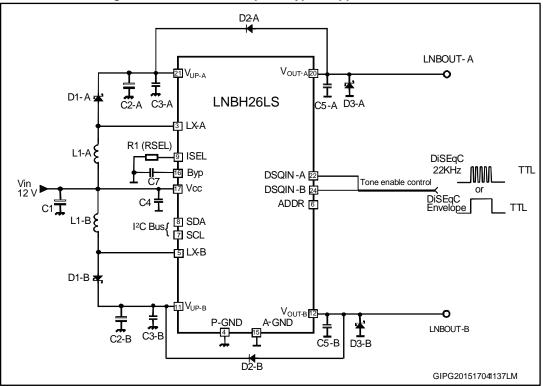

## 5 Typical application circuits

Figure 6: LNBH26LS DiSEqC 1.X typical application circuit

Table 5: LNBH26LS DiSEqC 1.x bill of material

| Component | Notes                                                                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Component | IAOTE2                                                                                                                                              |

| R1 (RSEL) | SMD resistor. Refer to <i>Table 12: "Electrical characteristics of section A/B"</i> and ISEL pin description in <i>Table 2: "Pin description"</i> . |

|           | > 25 V electrolytic capacitor, 100 µF or higher is suitable                                                                                         |

| C1        | or                                                                                                                                                  |

|           | > 25 V ceramic capacitor, 10 μF or higher is suitable.                                                                                              |

|           | With COMP = 0, > 25 V electrolytic capacitor, 100 μF or higher is suitable                                                                          |

| C2        | or                                                                                                                                                  |

| C2        | with COMP = 1, > 35 V ceramic capacitor, 22 μF (or 2 x 10 μF) or higher is                                                                          |

|           | suitable.                                                                                                                                           |

| C3        | From 470 nF to 2.2 µF ceramic capacitor placed as closer as possible to VUP pins.                                                                   |

|           | Higher values allow lower DC-DC noise.                                                                                                              |

| C5        | From 100 nF to 220 nF ceramic capacitor placed as closer as possible to VOUT                                                                        |

|           | pins. Higher values allow lower DC-DC noise.                                                                                                        |

| C4, C7    | 220 nF ceramic capacitors. To be placed as closer as possible to VOUT pin.                                                                          |

| D1        | STPS130A or similar Schottky diode.                                                                                                                 |

| D2        | 1N4001-07, S1A-S1M, or any similar general purpose rectifier.                                                                                       |

| D3        | BAT54, BAT43, 1N5818, or any low power Schottky diode with I <sub>F</sub> (AV) > 0.2 A,                                                             |

|           | $V_{RRM}$ > 25 V, $V_F$ < 0.5 V. To be placed as closer as possible to VOUT pin.                                                                    |

|           | With COMP=0, use 10 $\mu$ H inductor with $I_{SAT} > I_{PEAK}$ where $I_{PEAK}$ is the boost                                                        |

| L1        | converter peak current, or                                                                                                                          |

| -         | with COMP=1 and C2 = 22 $\mu$ F, use 6.8 $\mu$ H inductor with I <sub>SAT</sub> > I <sub>PEAK</sub> where I <sub>PEAK</sub> is                      |

|           | the boost converter peak current.                                                                                                                   |

DocID025504 Rev 2

LNBH26LS I<sup>2</sup>C bus interface

#### 6 I<sup>2</sup>C bus interface

Data transmission from the main microprocessor to the LNBH26LS, and vice versa, takes place through the 2-wire I<sup>2</sup>C bus interface, consisting of the 2-line SDA and SCL (pull-up resistors to positive supply voltage must be externally connected).

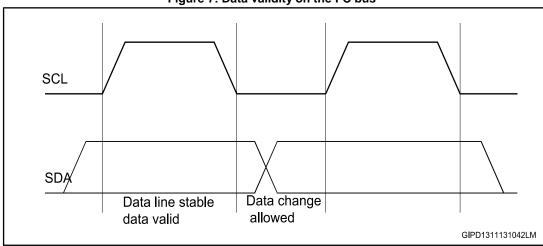

### 6.1 Data validity

As shown in *Figure 7: "Data validity on the I<sup>2</sup>C bus"*, the data on the SDA line must be stable during the high semi-period of the clock. The high and low state of the data line can only change when the clock signal on the SCL line is low.

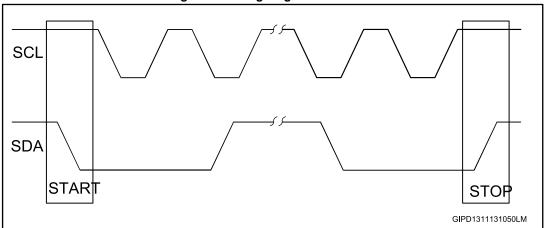

### 6.2 Start and stop condition

As shown in *Figure 8: "Timing diagram of I<sup>2</sup>C bus"*, a start condition is a transition from high to low of the SDA line while SCL is high. The stop condition is a transition from low to high of the SDA line while SCL is high. A stop condition must be sent before than each start condition.

### 6.3 Byte format

Every byte transferred to the SDA line must contain 8 bits. Each byte must be followed by an acknowledge bit. The MSB is the first to be transferred.

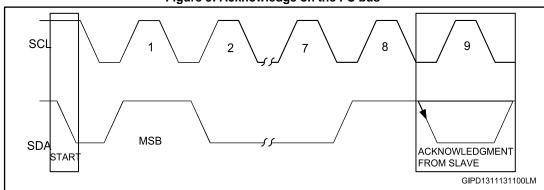

### 6.4 Acknowledge

The master (microprocessor) puts a resistive high level on the SDA line during the acknowledge clock pulse, see *Figure 9: "Acknowledge on the I²C bus"*. The peripheral (LNBH26LS), which acknowledges, must pull down (low) the SDA line during the acknowledge clock pulse, so that the SDA line is stable low during this clock pulse. The peripheral, which has been addressed, must generate acknowledge after the reception of each byte, otherwise the SDA line remains at the high level during the ninth clock pulse time. In this case, the master transmitter can generate the STOP information in order to abort the transfer. The LNBH26LS doesn't generate acknowledge if the  $V_{\rm CC}$  supply is below the undervoltage lockout threshold (4.7 V typ.).

### 6.5 Transmission without acknowledge

If the detection of LNBH26LS acknowledge is not necessary, the microprocessor can use a simpler transmission; it simply waits for one clock without checking the slave acknowledging, and sends the new data. This approach has less protection in case of misworking and decreases noise immunity.

I<sup>2</sup>C bus interface

Figure 7: Data validity on the I<sup>2</sup>C bus

Figure 8: Timing diagram of I<sup>2</sup>C bus

Figure 9: Acknowledge on the I<sup>2</sup>C bus

LNBH26LS I<sup>2</sup>C interface protocol

### 7 I<sup>2</sup>C interface protocol

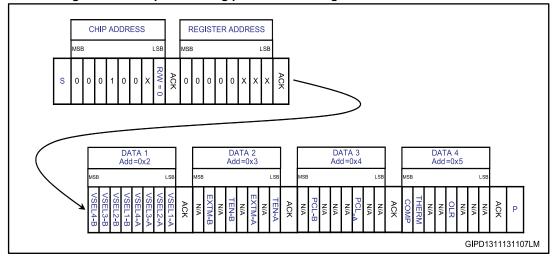

#### 7.1 Write mode transmission

The LNBH26LS interface protocol is made up of:

- A start condition (S)

- A chip address byte with the LSB bit R/W = 0

- A register address (internal address of the first register to be accessed)

- A sequence of data (byte to write to the addressed internal register + acknowledge)

- The following bytes, if any, to be written to successive internal x

- A stop condition (P), the transfer lasts until a stop bit is encountered

- The LNBH26LS, as slave, acknowledges every byte transfer

Figure 10: Example of writing procedure starting with first data address 0x2

ACK = acknowledge

S = start

P = stop

R/W = 1/0, read/write bit

X = 0/1, set the values to select the chip address, see *Table 13: "Output voltage selection table (data1 register, write mode)"* for pin selection and to select the register address, see *Table 6: "DATA 1 (read/write register. Register address = 0X2)"* and *Table 10: "STATUS 1 (read register. Register address = 0X0)"*.

The writing procedure can start from any register address by simply setting the X values in the register address byte (after the chip address). It can be also stopped by the master by sending a stop condition after any acknowledge bit.

I<sup>2</sup>C interface protocol

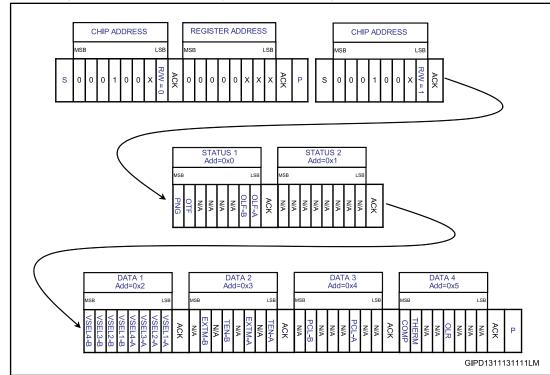

#### 7.2 Read mode transmission

In read mode the byte sequence must be as follows:

- A start condition (S)

- A chip address byte with the LSB bit R/W=0

- The register address byte of the internal first register to be accessed

- A stop condition (P)

- A new master transmission with the chip address byte and the LSB bit R/W=1

- After the acknowledge, the LNBH26LS starts sending the addressed register content.

As long as the master keeps the acknowledge low, the LNBH26LS transmits the next address register byte content

- The transmission is terminated when the master sets the acknowledge high with a following stop bit

Figure 11: Example of reading procedure starting with first status address 0X0

ACK = acknowledge

S = start

P = stop

R/W = 1/0, read/write bit

X = 0/1, set the values to select the chip address, see *Table 15: "Address pin characteristics"* for pin selection and to select the register address, see *Table 6: "DATA 1 (read/write register. Register address = 0X2)"*.

The reading procedure can start from any register address (STATUS 1, 2 or DATA 1..4) by simply setting the X values in the register address byte (after the first chip address in the above figure). It can be also stopped by the master by sending a stop condition after any acknowledge bit.

LNBH26LS I<sup>2</sup>C interface protocol

### 7.3 Data registers

The DATA 1..4 registers can be addressed both to write and read mode. In read mode they return the last writing byte status received in the previous write transmission.

The following tables provide the register address values of DATA 1..4 and a function description of each bit.

Table 6: DATA 1 (read/write register. Register address = 0X2)

| Bit         | Name    | СН | Value | Description                                        |

|-------------|---------|----|-------|----------------------------------------------------|

| Bit 0 (LSb) | VSEL1-A |    | 0/1   | Channel A                                          |

| Bit 1       | VSEL2-A | ٨  | 0/1   | output voltage selection bits                      |

| Bit 2       | VSEL3-A | Α  | 0/1   | refer to Table 13: "Output voltage selection table |

| Bit 3       | VSEL4-A |    | 0/1   | (data1 register, write mode)"                      |

| Bit 4       | VSEL1-B |    | 0/1   | Channel B                                          |

| Bit 5       | VSEL2-B | В  | 0/1   | output voltage selection bits                      |

| Bit 6       | VSEL3-B | В  | 0/1   | refer to Table 13: "Output voltage selection table |

| Bit 7 (MSb) | VSEL4-B |    | 0/1   | (data1 register, write mode)"                      |

N/A = reserved bit.

All bits reset to "0" at power-on.

Table 7: DATA 2 (read/write register. Register address = 0X3)

| Bit         | Name     | СН       | Value | Description                                                           |                                                                     |

|-------------|----------|----------|-------|-----------------------------------------------------------------------|---------------------------------------------------------------------|

| Bit 0 (LSb) | TEN A    |          | 1     | 22 kHz tone enabled. Tone output controlled by the DSQIN pin          |                                                                     |

|             |          |          | 0     | 22 kHz tone output disabled                                           |                                                                     |

| Bit 1       | N/A      |          | 0     | Reserved. Keep to "0"                                                 |                                                                     |

| Dit 2       | FXTM-A   | А        | 1     | DSQIN input pin is set to receive external 22 kHz TTL signal source   |                                                                     |

| Bit 2 EXTI  | EXTIVI-A | EXTIVI-A | 0     | DSQIN input pin is set to receive external DiSEqC envelope TTL signal |                                                                     |

| Bit 3       | N/A      |          | 0     | Reserved. Keep to "0"                                                 |                                                                     |

| Bit 4       | TEN-B    |          | 1     | 22 kHz tone enabled. Tone output controlled by the DSQIN pin          |                                                                     |

|             |          |          | 0     | 22 kHz tone output disabled                                           |                                                                     |

| Bit 5       | N/A      |          | 0     | Reserved. Keep to "0"                                                 |                                                                     |

| Bit 6       | EXTM-B   | EVTIA D  | В     | 1                                                                     | DSQIN input pin is set to receive external 22 kHz TTL signal source |

|             |          |          | 0     | DSQIN input pin is set to receive external DiSEqC envelope TTL signal |                                                                     |

| Bit 7 (MSb) | N/A      |          | 0     | Reserved. Keep to "0"                                                 |                                                                     |

N/A = reserved bit.

All bits reset to "0" at power-on.

I<sup>2</sup>C interface protocol LNBH26LS

Table 8: DATA 3 (read/write register. Register address = 0X4)

| Table 6. DATA 6 (read/write register, register, address = 0.4) |       |    |       |                                                             |

|----------------------------------------------------------------|-------|----|-------|-------------------------------------------------------------|

| Bit                                                            | Name  | СН | Value | Description                                                 |

| Bit 0 (LSb)                                                    | N/A   |    | 0     | Reserved. Keep to "0"                                       |

| Bit 1                                                          | N/A   |    | 0     | Reserved. Keep to "0"                                       |

| Bit 2                                                          | PCL-A |    | 1     | Pulsed (dynamic) LNB output current limiting is deactivated |

|                                                                |       | А  | 0     | Pulsed (dynamic) LNB output current limiting is active      |

| Bit 3                                                          | N/A   |    | 0     | Reserved. Keep to "0"                                       |

| Bit 4                                                          | N/A   |    | 0     | Reserved. Keep to "0"                                       |

| Bit 5                                                          | N/A   |    | 0     | Reserved. Keep to "0"                                       |

| Bit 6                                                          | PCL-B |    | 1     | Pulsed (dynamic) LNB output current limiting is deactivated |

|                                                                |       | В  | 0     | Pulsed (dynamic) LNB output current limiting is deactivated |

| Bit 7 (MSb)                                                    | N/A   |    | 0     | Reserved. Keep to "0"                                       |

N/A = reserved bit.

All bits reset to "0" at power-on.

LNBH26LS I<sup>2</sup>C interface protocol

Table 9: DATA 4 (read/write register. Register address = 0X5)

| Bit         | Name          | СН  | Value | Description                                                                                                                                                                                                                  |

|-------------|---------------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 0 (LSb) | N/A           | -   | 0     | Reserved. Keep to 0                                                                                                                                                                                                          |

| Bit 1       | N/A           | -   | 0     | Reserved. Keep to 0                                                                                                                                                                                                          |

| Bit 2       | N/A           | -   | 0     | Reserved. Keep to 0                                                                                                                                                                                                          |

|             | OI P          | Λ/D | 1     | In case of overload protection activation (OLF=1), all VSEL 14 bits are reset to "0" and LNB output (VOUT pin) is disabled. The VSEL bits must be set again by the master after the overcurrent condition is removed (OLF=0) |

| BIL 3       | Bit 3 OLR A/B |     | 0     | In case of overload protection activation (OLF=1) the LNB output (VOUT pin) is automatically enabled as soon as the overload condition is removed (OLF=0) with the previous VSEL bit setting                                 |

| Bit 4       | N/A           | -   | 0     | Reserved. Keep to 0                                                                                                                                                                                                          |

| Bit 5       | N/A           | -   | 0     | Reserved. Keep to 0                                                                                                                                                                                                          |

| Bit 6       | THERM         | A/B | 1     | If thermal protection is active (OTF=1), all VSEL 14 bits are reset to "0" and LNB output (VOUT pin) is disabled. The VSEL bits must be set again by the master after the overtemperature condition is removed (OTF=0)       |

| 0           |               |     | 0     | In case of thermal protection activation (OTF=1) the LNB output (VOUT pin) is automatically enabled as soon as the overtemperature condition is removed (OTF=0) with the previous VSEL bit setting                           |

| Rit 7 (MSP) | COMP          | -   | 1     | DC-DC converter compensation: set to use very low E.S.R. capacitors or ceramic caps on VUP pin                                                                                                                               |

| Bit 7 (MSB) | COMP          | -   | 0     | DC-DC converter compensation: set to use standard electrolytic capacitors on VUP pin                                                                                                                                         |

### 7.4 Status registers

The STATUS 1, 2 registers can only be addressed to read mode and provide the diagnostic functions described in the following tables.

Table 10: STATUS 1 (read register. Register address = 0X0)

| Bit           | Name  | СН     | Value | Description                                                                                                                                                                                                         |

|---------------|-------|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 0 (LSb)   | OLF-A | А      | 1     | VOUT pin overload protection has been triggered (I <sub>OUT</sub> > I <sub>LIM</sub> ). Refer to <i>Table 8: "DATA 3 (read/write register. Register address = 0X4)"</i> for the overload operation and PCL settings |

|               |       |        | 0     | No overload protection has been triggered to the VOUT pin ( $I_{OUT} < I_{LIM}$ )                                                                                                                                   |

| Bit 1 OLF-B B |       | 1<br>B |       | VOUT pin overload protection has been triggered (I <sub>OUT</sub> > I <sub>LIM</sub> ). Refer to <i>Table 8: "DATA 3 (read/write register. Register address = 0X4)"</i> for the overload operation and PCL settings |

|               |       |        | 0     | No overload protection has been triggered to VOUT pin (I <sub>OUT</sub> < I <sub>LIM</sub> )                                                                                                                        |

I<sup>2</sup>C interface protocol LNBH26LS

| Bit   | Name | СН      | Value | Description                                                                                                                                                           |

|-------|------|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 2 | N/A  | -       | -     | Reserved                                                                                                                                                              |

| Bit 3 | N/A  | -       | -     | Reserved                                                                                                                                                              |

| Bit 4 | N/A  | -       | -     | Reserved                                                                                                                                                              |

| Bit 5 | N/A  | -       | -     | Reserved                                                                                                                                                              |

| Bit 6 | OTF  | OTF A/B | 1     | Junction overtemperature is detected, $T_J > 150$ °C (typ.). See also THERM bit setting in <i>Table 9:</i> "DATA 4 (read/write register. Register address = $0X5$ )". |

|       |      |         | 0     | Junction overtemperature not detected, T <sub>J</sub> < 135 °C (typ.). T <sub>J</sub> is below thermal protection threshold                                           |

| Bit 7 | PNG  | G A/B   | 1     | Input voltage (VCC pin) lower than LPD minimum thresholds. Refer to <i>Table 12: "Electrical characteristics of section A/B"</i>                                      |

| (MSb) | PNG  |         | 0     | Input voltage (VCC pin) higher than LPD thresholds. Refer to <i>Table 12: "Electrical characteristics of section A/B"</i>                                             |

N/A = reserved bit.

All bits reset to "0" at power-on.

Table 11: STATUS 2 (read register. Register address = 0X1)

|                | Table 11: 01/1100 E (Toda Toglotof Rogiotof addition = 0/1) |    |       |             |  |  |

|----------------|-------------------------------------------------------------|----|-------|-------------|--|--|

| Bit            | Name                                                        | СН | Value | Description |  |  |

| Bit 0<br>(LSb) | N/A                                                         | -  | -     | Reserved    |  |  |

| Bit 1          | N/A                                                         | -  | -     | Reserved    |  |  |

| Bit 2          | N/A                                                         | -  | -     | Reserved    |  |  |

| Bit 3          | N/A                                                         | -  | 1     | Reserved    |  |  |

| Bit 4          | N/A                                                         | -  | 1     | Reserved    |  |  |

| Bit 5          | N/A                                                         | -  | 1     | Reserved    |  |  |

| Bit 6          | N/A                                                         | -  | 1     | Reserved    |  |  |

| Bit 7<br>(MSb) | N/A                                                         | -  | -     | Reserved    |  |  |

N/A = reserved bit.

All bits reset to "0" at power-on.

### 8 Electrical characteristics

Refer to Section 5: "Typical application circuits",  $T_J$  from 0 to 85 °C, all DATA 1..4 register bits set to 0 unless VSEL1 = 1, RSEL = 11 k $\Omega$ , DSQIN = low,  $V_{IN}$  = 12 V,  $I_{OUT}$  = 50 mA, unless otherwise stated. Typical values are referred to  $T_J$  = 25 °C.  $V_{OUT}$  =  $V_{OUT}$  pin voltage. See software description section for Section 6: "I²C bus interface" and Section 7: "I²C interface protocol".

Table 12: Electrical characteristics of section A/B

| Symbol            | Parameter                            | Test conditions                                                                                          | Min. | Тур.                 | Max. | Unit     |

|-------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------|------|----------------------|------|----------|

| V <sub>IN</sub>   | Supply voltage (1)                   |                                                                                                          | 8    | 12                   | 16   | V        |

|                   |                                      | Both sections A and B enabled,<br>Iout = 0 mA                                                            |      | 12                   |      |          |

| I <sub>IN</sub>   | Supply current                       | 22 kHz tone enabled<br>(TEN-A/B = 1, DSQIN-A/B = high), I <sub>OUT</sub> = 0<br>mA                       |      | 19                   |      | mA       |

|                   |                                      | Both sections A and B set in standby: VSEL1=VSEL2= VSEL3= VSEL4=0                                        |      | 2                    |      |          |

| V <sub>OUT</sub>  | Output voltage total accuracy        | Valid at any V <sub>OUT</sub> selected level                                                             | -3.5 |                      | +3.5 | %        |

| V <sub>OUT</sub>  | Line regulation                      | V <sub>IN</sub> = 8 to 16 V                                                                              |      |                      | 40   | mV       |

| V <sub>OUT</sub>  | Load regulation                      | I <sub>OUT</sub> from 50 to 500 mA                                                                       |      | 75                   | 100  |          |

| 1                 | Output current                       | RSEL = 15 kΩ                                                                                             | 500  |                      | 750  | mA       |

| I <sub>LIM</sub>  | limiting thresholds                  | RSEL = 20 kΩ                                                                                             | 350  |                      | 550  |          |

| I <sub>SC</sub>   | Output short-circuit current         | RSEL = 15 kΩ                                                                                             |      | 350                  |      | mA       |

| SS                | Soft-start time                      | V <sub>OUT</sub> from 0 to 13 V                                                                          |      | 4                    |      | ms       |

| SS                | Soft-start time                      | V <sub>OUT</sub> from 0 to 18 V                                                                          |      | 6                    |      | ms       |

| T13-18            | Soft transition rise time            | V <sub>OUT</sub> from 13 to 18 V                                                                         |      | 1.5                  |      | ms       |

| T18-13            | Soft transition fall time            | V <sub>OUT</sub> from 18 to 13 V                                                                         |      | 1.5                  |      | ms       |

| T <sub>OFF</sub>  | Dynamic overload protection OFF time | PCL = 0, output<br>shorted                                                                               |      | 900                  |      | ms       |

| T <sub>ON</sub>   | Dynamic overload protection ON time  | PCL = 0, output shorted                                                                                  |      | T <sub>OFF</sub> /10 |      |          |

| A <sub>TONE</sub> | Tone amplitude                       | DSQIN = high,<br>EXTM=0, TEN=1<br>I <sub>OUT</sub> from 0 to 500 mA<br>C <sub>BUS</sub> from 0 to 750 nF | 0.55 | 0.675                | 0.8  | $V_{PP}$ |

| Symbol                   | Parameter                             | Test conditions                                                                                               | Min. | Тур. | Max. | Unit |

|--------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------|------|------|------|------|

| F <sub>TONE</sub>        | Tone frequency                        | DSQIN = high,<br>EXTM=0, TEN=1                                                                                | 20   | 22   | 24   | kHz  |

| D <sub>TONE</sub>        | Tone duty cycle                       |                                                                                                               | 43   | 50   | 57   | %    |

| tr, tf                   | Tone rise or fall time (2)            |                                                                                                               | 5    | 8    | 15   | μs   |

| Eff <sub>DC/DC</sub>     | DC-DC converter efficiency            | I <sub>OUT</sub> = 500 mA                                                                                     |      | 93   |      | %    |

| F <sub>SW</sub>          | DC-DC converter switching frequency   |                                                                                                               |      | 440  |      | kHz  |

| UVLO                     | Undervoltage lockout thresholds       | UVLO threshold rising                                                                                         |      | 4.8  |      | V    |

|                          |                                       | UVLO threshold falling                                                                                        |      | 4.7  |      |      |

| $V_{LP}$                 | Low power diagnostic (LPD) thresholds | V <sub>LP</sub> threshold rising                                                                              |      | 7.2  |      | V    |

|                          |                                       | V <sub>LP</sub> threshold falling                                                                             |      | 6.7  |      |      |

| V <sub>IL</sub>          | DSQIN, pin logic low                  |                                                                                                               |      |      | 0.8  | V    |

| V <sub>IH</sub>          | DSQIN, pin logic high                 |                                                                                                               | 2    |      |      | V    |

| I <sub>IH</sub>          | DSQIN, pin input current              | V <sub>IH</sub> = 5 V                                                                                         |      | 15   |      | μΑ   |

| I <sub>OBK</sub>         | Output backward current               | All VSELx = 0, $V_{OBK}$ = 30 V                                                                               |      | -3   | -6   | mA   |

| I <sub>SINK</sub>        | Output low-side sink current          | V <sub>OUT</sub> forced at<br>V <sub>OUT_nom</sub> + 0.1 V                                                    |      | 70   |      | mA   |

| I <sub>SINK_TIME</sub> - | Low-side sink current time-out        | V <sub>OUT</sub> forced at V <sub>OUT_nom</sub> + 0.1 V                                                       |      | 10   |      | ms   |

| I <sub>REV</sub>         | Max. reverse current                  | V <sub>OUT</sub> forced at<br>V <sub>OUT_nom</sub> + 0.1 V,<br>after I <sub>SINK_TIME-OUT</sub> is<br>elapsed |      | 2    |      | mA   |

| T <sub>SHDN</sub>        | Thermal shutdown threshold            |                                                                                                               |      | 150  |      | °C   |

| DT <sub>SHDN</sub>       | Thermal shutdown hysteresis           |                                                                                                               |      | 15   |      | °C   |

#### Notes:

$<sup>^{(1)}</sup>$ In applications where (V<sub>CC</sub> - V<sub>OUT</sub>) > 1.3 V, the increased power dissipation, inside the integrated LDO, must be taken into account in the application thermal management design.

<sup>&</sup>lt;sup>(2)</sup>Guaranteed by design.

LNBH26LS Electrical characteristics

### 8.1 Output voltage selection

Each LNBH26LS channel is provided with 8 output voltage levels, (4 levels for 13 V range when VSEL4-A/B=0 and 4 levels for 18 V range when VSEL4-A/B=1) which can be selected through the register data1. The following table shows the output voltage values corresponding to VSELx bit combinations both for channel A and B. If all VSELx are at "0" the device is set in standby mode and the  $V_{OUT}$ -A/B are disabled.

Table 13: Output voltage selection table (data1 register, write mode)

| VSEL<br>4-A/B | VSEL<br>3-A/B | VSEL<br>2-A/B | VSEL<br>1-A/B | V <sub>OUT</sub> min. | V <sub>OUT</sub> -A/B<br>pin<br>voltage | V <sub>OUT</sub> max. | Function                                                                  |

|---------------|---------------|---------------|---------------|-----------------------|-----------------------------------------|-----------------------|---------------------------------------------------------------------------|

| 0             | 0             | 0             | 0             |                       | 0                                       |                       | V <sub>OUT</sub> -A/B disabled.<br>The LNBH26LS is set<br>in standby mode |

| 0             | 0             | 0             | 1             | 12.545                | 13.000                                  | 13.455                |                                                                           |

| 0             | 0             | 1             | 0             | 12.867                | 13.333                                  | 13.800                |                                                                           |

| 0             | 0             | 1             | 1             | 13.188                | 13.667                                  | 14.145                |                                                                           |

| 0             | 1             | 0             | 0             | 13.51                 | 14.000                                  | 14.490                |                                                                           |

| 1             | 0             | 0             | 0             | 17.515                | 18.150                                  | 18.785                |                                                                           |

| 1             | 0             | 0             | 1             | 17.836                | 18.483                                  | 19.130                |                                                                           |

| 1             | 0             | 1             | 0             | 18.158                | 18.817                                  | 19.475                |                                                                           |

| 1             | 0             | 1             | 1             | 18.48                 | 19.150                                  | 19.820                | _                                                                         |

$T_J$  from 0 to 85 °C,  $V_I$  = 12 V.

Table 14: I<sup>2</sup>C electrical characteristics

| Symbol           | Parameter                               | Test conditions                          | Min. | Тур. | Max. | Unit |

|------------------|-----------------------------------------|------------------------------------------|------|------|------|------|

| V <sub>IL</sub>  | Low level input voltage                 | SDA, SCL                                 |      |      | 0.8  | V    |

| V <sub>IH</sub>  | high level input voltage                | SDA, SCL                                 | 2    |      |      | V    |

| I <sub>IN</sub>  | Input current                           | SDA, SCL, $V_{IN} = 0.4$ to 4.5 V        | -10  |      | 10   | μΑ   |

| V <sub>OL</sub>  | Low level output voltage <sup>(1)</sup> | SDA (open drain), I <sub>OL</sub> = 6 mA |      |      | 0.6  | V    |

| F <sub>MAX</sub> | Maximum clock frequency                 | SCL                                      |      |      | 400  | kHz  |

#### Notes:

<sup>&</sup>lt;sup>(1)</sup>Guaranteed by design.

$T_J$  from 0 to 85 °C,  $V_I$  = 12 V.

Table 15: Address pin characteristics

| Symbol              | Parameter                                      | Test conditions                                                      | Min. | Тур. | Max. | Unit |

|---------------------|------------------------------------------------|----------------------------------------------------------------------|------|------|------|------|

| V <sub>ADDR-1</sub> | "0001000(R/W)"<br>address pin voltage<br>range | R/W bit determines the transmission mode: read (R/W=1) write (R/W=0) | 0    |      | 0.8  | ٧    |

| V <sub>ADDR-2</sub> | "0001001(R/W)"<br>address pin voltage<br>range | R/W bit determines the transmission mode: read (R/W=1) write (R/W=0) | 2    |      | 5    | ٧    |

LNBH26LS Package information

## 9 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: **www.st.com**. ECOPACK® is an ST trademark.

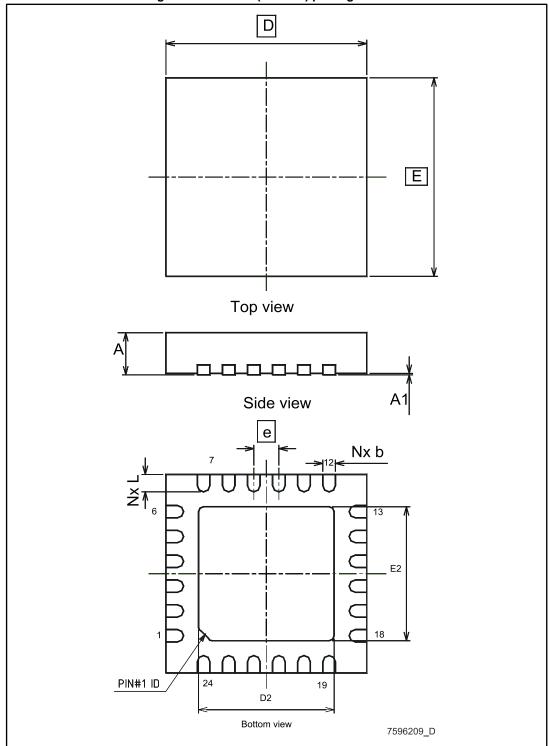

# 9.1 QFN24L (4x4 mm) package information

Figure 12: QFN24L (4x4 mm) package outline

Table 16: QFN24L (4x4 mm) package mechanical data

| Dim  | mm   |      |      |  |  |  |

|------|------|------|------|--|--|--|

| Dim. | Min. | Тур. | Max. |  |  |  |

| А    | 0.80 | 0.90 | 1.00 |  |  |  |

| A1   | 0.00 | 0.02 | 0.05 |  |  |  |

| b    | 0.18 | 0.25 | 0.30 |  |  |  |

| D    | 3.90 | 4.00 | 4.10 |  |  |  |

| D2   | 2.55 | 2.70 | 2.80 |  |  |  |

| Е    | 3.90 | 4.00 | 4.10 |  |  |  |

| E2   | 2.55 | 2.70 | 2.80 |  |  |  |

| е    | 0.45 | 0.50 | 0.55 |  |  |  |

| L    | 0.25 | 0.35 | 0.40 |  |  |  |

Figure 13: QFN24L (4x4 mm) recommended footprint

Package information LNBH26LS

# 9.2 QFN24L (4x4 mm) packing information

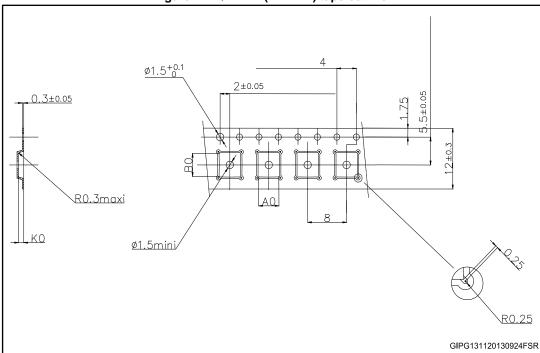

Figure 14: QFN24L (4x4 mm) tape outline

Table 17: QFN24L (4x4 mm) tape mechanical data

|      | ,    |

|------|------|

| Dim. | mm   |

| A0   | 4.35 |

| В0   | 4.35 |

| K0   | 1.1  |

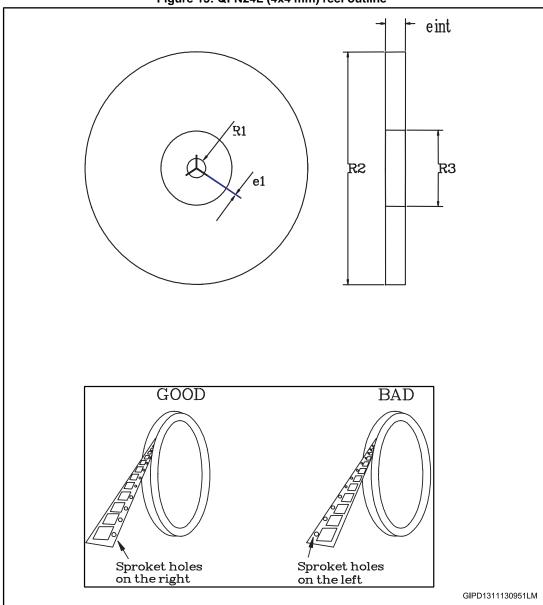

Figure 15: QFN24L (4x4 mm) reel outline

Table 18: QFN24L (4x4 mm) reel mechanical data

| Dim.     | R1 | R2  | R3 |

|----------|----|-----|----|

| Reel 13" | 13 | 330 | 60 |

Revision history LNBH26LS

# 10 Revision history

**Table 19: Document revision history**

| Date        | Revision | Changes                                                                      |  |

|-------------|----------|------------------------------------------------------------------------------|--|

| 04-Dec-2013 | 1        | Initial release.                                                             |  |

| 20-Apr-2015 | 2        | Updated section 2.11. Updated package information section. Changed figure 6. |  |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics - All rights reserved